# QUAD TWO-INPUT OR GATE

# GENERAL DESCRIPTION

The 7432 is a quad 2-input OR gate utilizing TTL (Transistor-Transistor-Logic) to provide the basic functions used in the implementation of digital integrated circuit systems. The device is completely compatible with all  $\alpha$  her Series 74 devices.

#### **FEATURES**

- Popular digital logic block

- Saves inverter function when sign inversion is not needed

# ABSOLUTE MAXIMUM RATINGS

| Supply Voltage                       | 5.25V         |

|--------------------------------------|---------------|

| Input Voltage                        | 5.5V          |

| Output Voltage                       |               |

| Operating Temperature Range:         |               |

| Storage Temperature Range            | 65°C to 150°C |

| Lead Temperature (Soldering, 10 sec) |               |

# BCD TO DECIMAL DECODER/DRIVER

# GENERAL DESCRIPTION

The 7441 is monolithic binary-coded-decimal to decimal decoder. The BCD number to be decoded is applied to the four input lines; and the unique output corresponding to the decimal equivalent of the input number falls to a logical 0 level. Outputs are designed to drive gas-filled-readout tubes but are also able to operate with other low current lamps and relays.

An over-range feature provides that if binary numbers between 10 and 15 are applied to the input the least significant bit of these numbers (0 through 5) will be decoded on the output.

### **FEATURES**

- Drive cold-cathode, numeric indicator tubes directly

- Fully decoded inputs

- Low leakage current 1.8 µ A @ 50V

- Low power dissipation 105 mW typical

# ABSOLUTE MAXIMUM RATINGS

| Supply Voltage (V <sub>CC</sub> )    | 5.25V |

|--------------------------------------|-------|

| Output Voltage                       |       |

| Input Voltage                        |       |

| Operating Temperature Range          |       |

| Storage Temperature Range            |       |

| Lead Temperature (Soldering, 10 sec) |       |

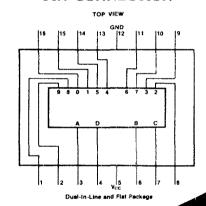

LOGIC DIAGRAM

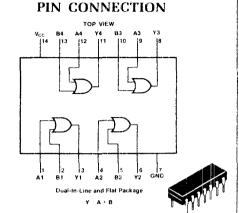

# PIN CONNECTION

## TRUTH TABLE

|              | INF | UТ |   | LOW OUTPUT |

|--------------|-----|----|---|------------|

| D            | С   | В  | A |            |

| 0            | 0   | 0  | 0 | 0          |

| 0            | 0   | 0  | 1 | 1          |

| 0            | 0   | 1  | 0 | 2          |

| 0            | 0   | 1  | 1 | 3          |

| 0            | 1   | 0  | 0 | 4          |

| 0            | 1   | 0  | 1 | 5          |

| 0            | 1   | 1  | 0 | 6          |

| 0            | 1   | 1  | 1 | 7          |

| 1            | 0   | 0  | 0 | 8          |

| 1            | 0   | 0  | 1 | 9          |

| (OVER RANGE) |     |    |   |            |

| 1            | 0   | 1  | 0 | 0          |

| 1            | 0   | 1  | 1 | 1          |

| 1            | 1   | 0  | 0 | 2          |

| 1            | 1   | 0  | 1 | 3          |

| 1            | 1   | 1  | 0 | 4          |

| 1            | 1   | 1  | 1 | 5          |